# VBIC95, The Vertical Bipolar Inter-Company Model

Colin C. McAndrew, Senior Member, IEEE, Jerold A. Seitchik, Member, IEEE, Derek F. Bowers, Senior Member, IEEE, Mark Dunn, Mark Foisy, Member, IEEE, Ian Getreu, Senior Member, IEEE, Marc McSwain, Shahriar Moinian, Member, IEEE, James Parker, David J. Roulston, Senior Member, IEEE, Michael Schröter, Member, IEEE, Paul van Wijnen, and Lawrence F. Wagner, Member, IEEE

Abstract— This paper details the VBIC95 bipolar junction transistor (BJT) model. The model was developed as an industry standard replacement for the SPICE Gummel-Poon (SGP) model, to improve deficiencies of the SGP model that have become apparent over time because of the advances in BJT process technology. VBIC95 is still based on the Gummel-Poon formulation, and thus can degenerate to be similar to the familiar SGP model. However, it includes improved modeling of the Early effect, quasi-saturation, substrate and oxide parasitics, avalanche multiplication, and temperature behavior that can be invoked selectively based on model parameter values.

#### I. INTRODUCTION

SINCE SPICE2 [1] helped usher IC design into the era of simulation, there has been an explosive growth in the number of MOSFET models available and used for circuit design. With over 50 MOSFET models in HSPICE, this growth may have gone a little overboard. But for bipolar junction transistors (BJT's), the pendulum has not so much swung the other way as it has become stuck. The SPICE Gummel–Poon (SGP) model [1] and [2] is still the only BJT model widely available and used for IC design. For modern BJT's, the SGP model is not sufficiently accurate for low risk design.

The formulation of the Gummel–Poon (GP) model accounts for the key physical parameters and mechanisms that control BJT behavior in an intuitive and consistent manner. However, the approximations that underlie the SGP model ignore effects that are important for accurate modeling of today's BJT's. The simplified SGP Early effect model is inaccurate for  $g_o$  (output conductance) modeling, and collector resistance modulation is ignored. Parasitic substrate transistor action, parasitic capacitances of base-emitter overlap in double poly BJT's, avalanche multiplication, and self-heating are not modeled, and the modeling of high frequency and temperature effects is inadequate.

Manuscript received February 15, 1996; revised June 27, 1996.

- C. C. McAndrew is with Motorola, Tempe, AZ 85284 USA.

- J. A. Seitchik is with Texas Instruments, Dallas, TX 75265 USA.

- D. F. Bowers is with Analog Devices, Sunnyvale. CA 94087 USA.

- M. Dunn is with Hewlett-Packard, Santa Rosa, CA 95043 USA.

- M. Foisy is with Motorola, Austin, TX 78721 USA.

- I. Getreu is with Analogy, Beaverton, OR 97075 USA

- M. McSwain is with MetaSoftware, Campbell, CA 95008 USA.

- S. Moinian is with AT&T Bell Laboratories, Reading, PA 19612 USA. J. Parker is with National Semiconductor, Santa Clara, CA 95052 USA

- D. J. Roulston is with the University of Waterloo, Waterloo, ON, N2L 3G1 Canada.

- M. Schröter is with Bell Northern Research, Kanata, ON, Canada.

- P. van Wijnen is with Intel/Philips, Santa Clara, CA 95052 USA. L. F. Wagner is with IBM. Hopewell Junction, NY 12533 USA.

- Publisher Item Identifier S 0018-9200(96)07329-5.

BJT models that overcome some of these problems have been published, e.g., [3]–[7], but have not become widely available and used. Dr. J. Shier, for years the driving force behind the IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), responded to complaints from meeting attendees about the lack of progress in making improved BJT models generally available by initiating a committee to address the problem. The result is the VBIC95 model, reported here and at BCTM 1996, and a commitment from major CAD vendors to implement VBIC95 in their circuit simulators. VBIC95 addresses the shortcomings of the SGP model noted above and is public domain. Complete source code is available.

Besides improving on the SGP model, VBIC95 was required to be as similar as possible to the SGP model so that it could leverage existing experience in BJT modeling and characterization. This was done by including advanced modeling features that are enabled and disabled by setting parameter values. The advantages of smooth, continuous models that do not use conditional statements to define separate operating regions have become recognized over the past decade, and VBIC95 is, apart from selectable backward compatibility with the SGP model, single-piece and  $C_{\infty}$ -continuous.

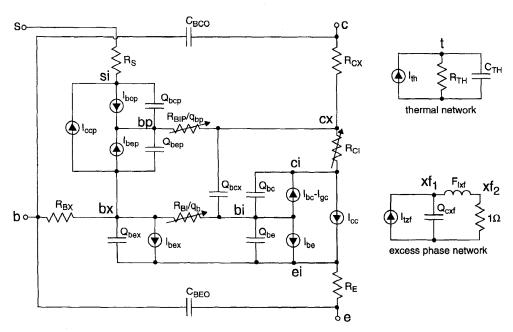

Fig. 1 shows the equivalent circuit for VBIC95. The model includes an intrinsic BJT (an npn will be used here) based on the Gummel–Poon model, and a parasitic BJT (pnp), modeled with a partial Gummel–Poon model. Excess phase is modeled through a second order network, and self-heating (not detailed here) is modeled by including the effects of a local temperature rise on the branch constituent relationships for each network element and adding a thermal network to model the local temperature rise.

Branch voltages are denoted:  $V_{bei} = V_{bi} - V_{ei}$ ,  $V_{bci} = V_{bi} - V_{ci}$ ,  $V_{bcx} = V_{bi} - V_{cx}$ ,  $V_{bep} = V_{bx} - V_{bp}$ ,  $V_{bcp} = V_{si} - V_{bp}$ ,  $V_{beo} = V_{b} - V_{e}$ , and  $V_{bco} = V_{b} - V_{c}$ , where  $V_{bi}$  is the voltage on node "bi" in Fig. 1, and so on.

#### II. INTRINSIC GUMMEL-POON MODEL

The forward transport current is [2]

$$I_{cc} = \frac{I_{tf} - I_{tr}}{q_b}$$

$$I_{tf} = I_S \left[ \exp\left(\frac{V_{bei}}{N_F V_{tv}}\right) - 1 \right]$$

$$I_{tr} = I_S \left[ \exp\left(\frac{V_{bci}}{N_R V_{tv}}\right) - 1 \right]$$

(1)

where  $I_{tf}$  and  $I_{tr}$  are the forward and reverse transport

Fig. 1. Equivalent network for VBIC95.

currents and  $V_{tv}=kT/q$ . Separate nonideality factors  $N_F$  and  $N_R$  are included for forward and reverse components of  $I_{cc}$ , for compatibility with the SGP model. However, we recommend using  $N_F=N_R$ , otherwise the model can become nonpassive.

The normalized base charge  $q_b$  in (1) is modeled using depletion and diffusion charge components, and not with the approximate linearized depletion charges used in the SGP model, so

$$q_{b} = q_{1} + \frac{q_{2}}{q_{b}}$$

$$q_{1} = 1 + \frac{q_{je}}{V_{ER}} + \frac{q_{jc}}{V_{EF}}$$

$$q_{2} = \frac{I_{tf}}{I_{KF}} + \frac{I_{tr}}{I_{KR}}$$

(2)

where the  $b{-}e$  and  $b{-}c$  depletion charges are

$$q_{je} = q_j(V_{bei}, P_E, M_E)$$

$q_{jc} = q_j(V_{bei}, P_C, M_C).$  (3)

Here,  $V_{EF}$  and  $V_{ER}$  are forward and reverse Early voltages,  $I_{KF}$  and  $I_{KR}$  are forward and reverse knee currents, and  $P_E$ ,  $P_C$  and  $M_E$ ,  $M_C$  are the built-in potentials and grading coefficients of the  $b{-}e$  and  $b{-}c$  junctions.  $q_1$  is smoothly limited to be greater than 0.0001, to avoid numerical problems.

VBIC95 has two models for the depletion charge function  $q_j$ . The standard SGP piecewise model and a single-piece model for which the capacitance smoothly limits to a constant value for junction biases greater than the built-in potential.

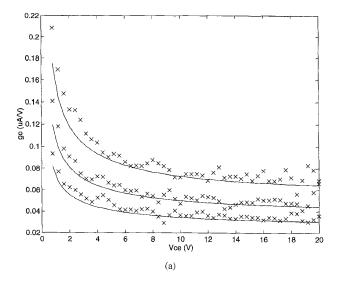

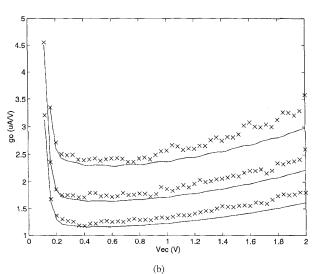

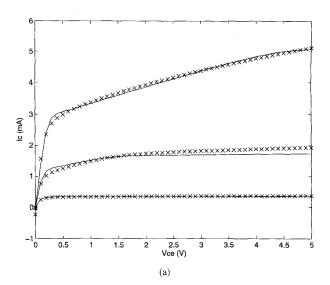

Fig. 2 shows  $g_o$  modeling for VBIC95 for both forward and reverse operation, for three values of base bias. SGP (not shown in Fig. 2) models  $g_o$  as a constant, whereas VBIC95 models the bias dependence of  $g_o$ . Fig. 3 shows  $g_o/I_e$  from reverse output characteristics, SGP cannot model the nonmonotonic variation with bias. The inaccuracies arise because of the linearized Early effect model  $(g_1)$  used in

SGP, compared to the proper depletion charge based model of VBIC95.

The b-e depletion charge is modeled as  $C_{JE}q_{je}$  and is partitioned between  $Q_{be}$  and  $Q_{bex}$  as  $W_{BE}$  and  $1-W_{BE}$ , where  $W_{BE}$  is a parameter which varies from one to zero, and to a first-order model's distributed base effects.  $Q_{be}$  also includes a diffusion charge component  $\tau_F I_{tf}$ , where  $\tau_F$  is modeled as in the SGP model. Improved  $\tau_F$  models have been reported [8], however the SGP model is still reasonable and so was retained for compatibility, for the present.  $Q_{bc}$  includes a depletion charge term  $C_{JC}q_{jc}$  and a diffusion charge term  $\tau_R I_{tr}$ , and an additional depletion charge term, detailed below, that models charge associated with the base pushing out into the collector.

Comparison of the  $q_b$ ,  $Q_{be}$ , and  $Q_{bc}$  models shows that

$$C_{JE}V_{ER} = C_{JC}V_{EF} \frac{A_e}{A_b}$$

$$= \tau_F I_{KF}$$

$$= \tau_R I_{KR}$$

$$\approx Q_{b0} \tag{4}$$

should hold, where  $A_e$  and  $A_b$  are the areas of the b-e and b-e junctions, and  $Q_{b0}$  is the base Gummel number. For modeling flexibility and separation of dc and ac modeling, the relationship (4) is not enforced in VBIC95.

The b-e component of base current comprises ideal and nonideal components

$$I_{bt} = I_{BEI} \left[ \exp\left(\frac{V_{bei}}{N_{EI}V_{tv}}\right) - 1 \right] + I_{BEN} \left[ \exp\left(\frac{V_{bei}}{N_{EN}V_{tv}}\right) - 1 \right]$$

(5)

and is, like the b-e depletion charge, partitioned between  $I_{be}$  and  $I_{bex}$  as  $W_{BE}$  and  $1-W_{BE}$  to model, to a first order, the distributed nature of the base. Similarly the b-c component of

Fig. 2. (a)  $g_o$  from forward output data and (b)  $g_o$  from reverse output data  $\times \times \times$  data, solid line VBIC95.

base current  $I_{bc}$  includes ideal and nonideal components. The physical mechanism that controls base current, recombination, and generation in the base and emitter for  $I_{bt}$  is separate from the mechanism that controls collector current, transport physics, and the base charge, so unlike SGP, in VBIC95 the two currents are not linked by a phenomenological beta parameter. This, in the future, will allow improved modeling of process variation and geometry effects.

The b-c component of base current also includes a weak avalanche component [9]

$$I_{gc} = (I_{cc} - I_{bc}) A_{VC1} (P_C - V_{bci})$$

$$\cdot \exp \left[ -A_{VC2} (P_C - V_{bci})^{ME-1} \right]$$

(6)

where  $A_{VC1}$  and  $A_{VC2}$  are model parameters.

Excess phase in VBIC95 modifies  $I_{tf}$  as follows.  $I_{tzf}$  in Fig. 1 is  $I_{tf}$  from (1). If the capacitance of the charge element  $Q_{cxf}$  is C and the inductance of the flux element  $F_{lxf}$  is L,

Fig. 3.  $g_o/I_c$  from reverse output data.  $\times \times \times$  data, solid line VBIC95, dashed line SGP.

then the voltage at node  $xf_2$  is

$$V_{xf2} = \frac{\frac{1}{LC}}{s^2 + \frac{s}{L} + \frac{1}{LC}} \tag{7}$$

which, on setting  $L = T_D/3$  and  $C = T_D$ , where  $T_D = 1/w_0$  is a parameter of VBIC95, is just the second-order Bessel polynomial approximation to excess phase of [10].  $V_{xf2}$  is then used as  $I_{tf}$  in  $I_{cc}$ . This implementation is consistent between ac and transient analyzes and is independent of the numerical algorithm used for integration.

# III. PARASITIC PARTIAL GUMMEL-POON MODEL

The transport current  $I_{ccp}$  of the parasitic transistor is modeled similarly to  $I_{cc}$ . Because the parasitic is distributed between intrinsic (under the emitter) and extrinsic (not under the emitter) components, the control of the forward component of  $I_{ccp}$  is split between  $V_{bep}$  and  $V_{bci}$  as

$$I_{tfp} = I_{SP} \left[ W_{SP} \exp \left( \frac{V_{bep}}{N_{FP}V_{tv}} \right) + (1 - W_{SP}) \exp \left( \frac{V_{bci}}{N_{FP}V_{tv}} \right) - 1 \right].$$

(8)

The normalized base charge of the parasitic only includes high-level forward injection

$$q_{bp} = 1 + \frac{q_{2p}}{q_{bp}}$$

$$q_{2p} = \frac{I_{tfp}}{I_{KP}}$$

$$(9)$$

as the Early effects and high level reverse injection are not important to model the behavior of the parasitic.

The charge elements associated with the parasitic transistor include depletion components, and a diffusion charge component  $\tau_R I_{tfp}$  is added to  $Q_{bep}$ . The base current components of the parasitic include ideal and nonideal components, modeled similarly to the base current components of the intrinsic device.

#### IV. INTRINSIC COLLECTOR MODELING

The modeling of the current in the intrinsic collector (epi) region is based on the analysis of [4]. Although the model of [4] has been adopted in the major commercial SPICE simulators, it has only recently becoming widely known that the model of [4] can predict negative  $g_o$  at high  $V_{be}$ . If the velocity saturation model in [4] is ignored, then the current in the epi is

$$I_{\text{epi0}} = \left\{ \frac{V_{rci} + V_{tv} \left[ K_{bci} - K_{bcx} - \log_e \left( \frac{K_{bci} + 1}{K_{bcx} + 1} \right) \right]}{R_{CI}} \right\}$$

$$K_{bci} = \left[ 1 + \gamma \exp\left( \frac{V_{bci}}{V_{tv}} \right) \right]^{1/2}$$

$$K_{bcx} = \left[ 1 + \gamma \exp\left( \frac{V_{bcx}}{V_{tv}} \right) \right]^{1/2}$$

(10)

where  $V_{rci} = V_{bci} - V_{bcx}$ . In [4], this is coupled with a velocity saturation model  $\mu = \mu_0/(1+\mu_0|\nabla\phi_e|v_{\rm sat})$  where  $v_{\rm sat}$  is the electron saturation speed. This modifies the denominator above to become  $R_{CI}(1+|V_{rci}|/V_O)$  where  $V_O = w_{\rm epi}v_{\rm sat}/\mu_0$ . This velocity saturation model is undesirable because it introduces discontinuities in high-order derivatives and because it causes the negative  $g_o$ . By using the alternative model  $\mu = \mu_0/[1+(\mu_0\nabla\phi_e/v_{\rm sat})^2]^{1/2}$ , and by using  $I_{\rm epi0}R_{CI}$  instead of  $V_{rci}$  in this model, both of the problems are overcome. Further, we empirically change  $V_O$  with  $V_{rci}$ , through the high  $R_C$  parameter  $H_{RCF}$ , to account for the increase in collector current with increases  $V_{rci}$  at high  $V_{bci}$ . The final model for the current in  $R_{CI}$  is

$$I_{rci} = \left( \frac{I_{epi0}}{1 + \frac{I_{epi0}R_{CI}}{V_O \left[ 1 + \frac{0.5(V_{rci}^2 + 0.01)^{1/2}}{V_O H_{RCF}} \right]} \right)^2$$

(11)

where a smooth approximation to  $|V_{rci}|$  has been used to avoid numerical problems and preserve high order continuity.

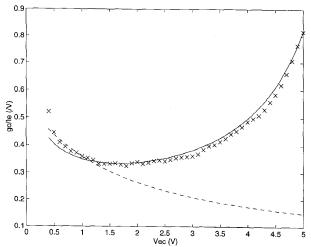

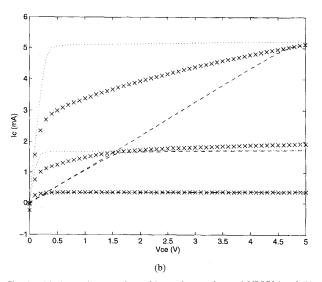

Fig. 4(a) shows a fit of VBIC95 to forward output data that includes significant quasi-saturation effects. For comparison, Fig. 4(b) shows that same data fitted by the SGP model. Because SGP includes a fixed collector resistance, it cannot fit the region where collector resistance modulation is occurring properly. The dashed line is SGP with a value of  $R_C$  chosen to model the onset of quasi-saturation reasonably, and the dotted line is SGP with  $R_C$  chosen to model deep saturation behavior reasonably. The improvement with VBIC95 is clear.

$Q_{bc}$  includes a component  $Q_{CO}K_{bci}$ , which models part of the charge associated with base pushout [4]. The other part is  $Q_{bcx} = Q_{CO}K_{bcx}$ .

#### V. PARASITIC RESISTANCE AND CAPACITANCE MODELING

To model constant b-e and b-c overlap capacitances, which are important for modern double poly BJT's, VBIC95 includes the linear overlap capacitors  $C_{BEO}$  and  $C_{BCO}$ . Emitter,

Fig. 4. (a) Forward output data with quasi-saturation and VBIC95 and (b) forward output data with quasi-saturation and SGP.  $\times$   $\times$  data, solid line VBIC95, dashed line SGP with high  $R_C$ , dotted line SGP with low  $R_C$ .

substrate, and extrinsic base and collector resistances are modeled as linear resistors. The base resistances of the intrinsic and parasitic transistors are bias dependent, with their resistances modulated by the normalized base charges. The SGP model allows selection of either a  $q_b$  modulated intrinsic base resistance  $R_{BI}$ , or  $R_{BI}$  modified with bias to account for emitter crowding. Both mechanisms occur in practice, but no model that accurately includes both effects, over geometry, is available at present. The base partitioning by  $W_{BE}$  to a first-order models some emitter crowding effects, so the  $q_b$  modulation model is used in VBIC95.

### VI. TEMPERATURE MAPPINGS

BJT electrical behavior varies with temperature, and so VBIC95 has temperature mappings defined for its model parameters. The mappings are similar to, but improved on, the temperature mappings for the SGP model.

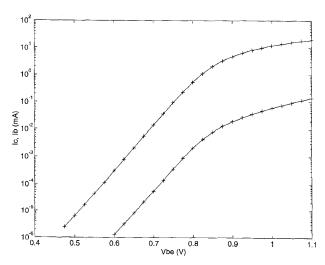

Fig. 5. Forward Gummel characteristics. + + + data, solid line VBIC95.

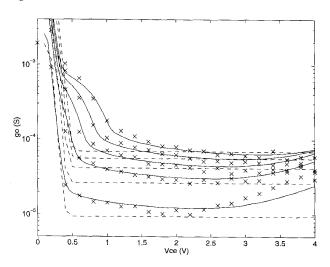

Fig. 6. Output conductance affected by quasi-saturation and avalanche multiplication.  $\times \times \times$  data, solid line VBIC95, dashed line SGP.

The resistances have a temperature variation

$$R(T_2) = R(T_1) \left(\frac{T_2}{T_1}\right)^{XR} \tag{12}$$

where the temperatures are in Kelvin, and there is a separate  $X_R$  parameter for each doping type region.

The transport saturation current varies as

$$I_S(T_2) = I_S(T_1) \left\{ r_T^{XIS} \exp\left[ -E_A \frac{(1 - r_T)}{V_{tv}} \right] \right\}^{1/NF}$$

(13)

where  $r_T = T_2/T_1$  and  $X_{IS}$  and  $E_A$  are parameters. This is similar to the SGP model and is based on the variation of  $n_{ie}^2$  with temperature. The other saturation currents have similar temperature mappings, with separate activation energies for ideal and nonideal components. This allows fitting of  $\beta_F$  and  $\beta_R$  over bias and temperature.

The junction built-in potentials P vary with temperature as  $(kT/q)\log_e{(n_{n0}p_{p0}/n_{ie}^2)}$ , which is similar to the SGP model, but avoids the problem with the SGP model of the

TABLE I

COMPARISON OF S-PARAMETER FITS

| s-parameter          | SGP RMS % error | VBIC95 RMS % error |

|----------------------|-----------------|--------------------|

| re(S <sub>11</sub> ) | 99.9            | 7.0                |

| im(S <sub>11</sub> ) | 65.2            | 6.2                |

| re(S <sub>12</sub> ) | 112.6           | 12.0               |

| im(S <sub>12</sub> ) | 34.6            | 6.9                |

| re(S <sub>21</sub> ) | 209.6           | 14.3               |

| im(S <sub>21</sub> ) | 81.6            | 8.3                |

| re(S <sub>22</sub> ) | 31.3            | 8.5                |

| im(S <sub>22</sub> ) | 63.8            | 8.5                |

potentials becoming negative as temperature increases. The zero bias junction capacitances vary as where M is the junction grading coefficient. The parameter  $\gamma$  in the quasi-sat model is proportional to  $n_{ie}^2$  [4], and so varies with temperature as (13).  $V_O$  is modeled similarly to (12), with parameter  $X_{VO}$ , and  $N_F$ ,  $N_R$ , and  $A_{VC2}$  are modeled as varying linearly with temperature.

## VII. EXAMPLES

Figs. 2-4 show the accuracy of VBIC95 for modeling  $g_o$  (i.e., for modeling the Early effect) and for modeling quasi-saturation. Fig. 5 shows a fit of VBIC95 to forward Gummel data. Fig. 6 shows a comparison of  $g_o$  modeling by VBIC95 and by SGP. The improvement VBIC95 offers over SGP is clear, and is due to the collector resistance modulation model, the proper Early effect model, and the weak avalanche model. All of these effects were inherent in the measured data of Fig. 6.

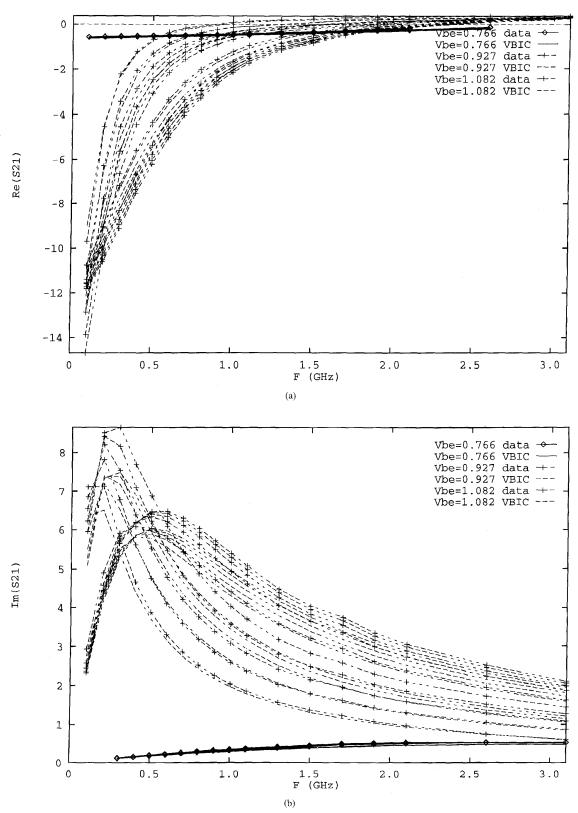

Fig. 7 shows fits of VBIC95 to  $S_{21}$  data, over a range of  $V_{be}$  and  $V_{ce}$  values. The different trend in the shape of the curves over bias and frequency is apparent and is modeled by VBIC95. Table I compares rms errors over bias and frequency between VBIC95 and SGP. The models were optimized in the same optimization tool to the same data.

#### VIII. CONCLUSIONS

In this paper we have detailed the VBIC95 BJT model and provided examples that show how it improves on the SGP model. VBIC95 was developed to provide a public domain BJT model suitable for accurate simulation of circuits being designed in modern IC bipolar technologies. A significant emphasis is "public domain," and this not only means that the model code and associated test programs are available, but that CAD suppliers were involved in the model development and have committed to implementing VBIC95 in their simulators and that extraction algorithms are also available. These are still under development and were reviewed in [11].

Commercial versions of VBIC95 will be available through Analogy, Cadence, HP, Meta-Software, Microsim, and Silvaco, and VBIC95 will also be available in proprietary AT&T and Motorola circuit simulators. Extraction routines will be available from HP, Silvaco, and TMA.

Complete source code for VBIC95, with a stand-alone solver and test results for verification of implementations, is available from mcandrew@sst.sps.mot.com.

Fig. 7.  $S_{21}$  data and VBIC95 fit.

#### REFERENCES

- L. W. Nagel, "SPICE2: A computer program to simulate semiconductor circuits," Memo. no. ERL-M520, Electronics Research Laboratory, University of California, Berkeley, May 1975.

- [2] H. K. Gummel and H. C. Poon, "An integrated charge control model of bipolar transistors," *Bell Syst. Tech. J.*, vol. 49, pp. 827–852, May 1970.

- [3] L. J. Turgeon and J. R. Mathews, "A bipolar transistor model of quasisaturation for use in computer-aided design (CAD)," in *Proc.* 1980 IEDM, pp. 394–397.

- [4] G. M. Kull, L. W. Nagel, S.-W. Lee, P. Lloyd, E. J. Prendergast, and H. K. Dirks, "A unified circuit model for bipolar transistors including quasi-saturation effects," *IEEE Trans. Electron Devices*, vol. 32, no. 6, pp. 1103–1113, June 1985.

- [5] H. C. de Graaff and W. J. Kloosterman, "New formulation of the current and charge relations in bipolar transistors for modeling for CACD purposes," *IEEE Trans. Electron Devices*, vol. 32, no. 11, pp. 2415–2419, Nov. 1985.

- [6] H. Stubing and H.-M. Rein, "A compact physical large-signal model for high-speed bipolar transistors at high current densities—Part I: onedimensional model," *IEEE Trans. Electron Devices*, vol. 34, no. 8, pp. 1741–1751. Aug. 1987.

- 1741–1751, Aug. 1987.

[7] H. Jeong and J. G. Fossum, "A charge-based large-signal bipolar transistor model for device and circuit simulation," *IEEE Trans. Electron Devices*, vol. 34, no. 1, pp. 124–131. Jan. 1989.

- Devices, vol. 34, no. 1, pp. 124–131, Jan. 1989.

[8] M. Schröter and H.-M. Rein, "Transit time of high-speed bipolar transistors in dependence on operating point, technological parameters, and temperature," in Proc. 1989 BCTM, pp. 250–253.

[9] W. J. Kloosterman and H. C. de Graaff, "Avalanche multiplication in a

- [9] W. J. Kloosterman and H. C. de Graaff, "Avalanche multiplication in a compact bipolar transistor model for circuit simulation," in *Proc. 1988* BCTM, pp. 103–106.

- [10] P. B. Weil and L. P. McNamee, "Simulation of excess phase in bipolar transistors," *IEEE Trans. Circuits Syst.*, vol. 25, no. 2, pp. 114–116, Feb. 1978.

- [11] J. Parker and M. Dunn, "VBIC 95 bipolar transistor model and associated parameter extraction," 1995 HP EEsof US IC-CAP User's Meeting.

Colin C. McAndrew (S'82–M'84–SM'90) received the B.E. degree in electrical engineering from Monash University, Melbourne, Vic., Australia, in 1978, and the M.A.Sc. and Ph.D. degrees in systems design engineering from the University of Waterloo, Waterloo, ON, Canada, in 1982 and 1984, respectively.

Since 1995, he has been the Manager of the Statistical Modeling and Characterization Laboratory at Motorola, Tempe, AZ. From 1987 to 1995, he was a Member of Technical Staff at AT&T Bell Laboratories, Allentown, PA. From 1978 to 1980 and 1984 to 1987, he was an engineer at the Herman Research Laboratory of the State Electricity Commission of Victoria.

Dr. McAndrew was awarded the Ian Langlands Medal of the IE Australia for 1978.

**Jerold A. Seitchik** (M'77) obtained the B.S. in physics from the University of Delaware in 1956 and the Ph.D. in physics at the University of Pennsylvania in 1962.

He is a senior member of the technical staff at Texas Instrument's Semi-conductor Process and Device Laboratory (SPDC). He assumed responsibility determining the vulnerability of semi-conductor circuits to neutron and alpha-particle induced errors. He continues to guide the bipolar predictive modeling program in SPDC and to be responsible for the development of new bipolar characterization methodologies. These activities include upgrading the bipolar modeling tools and utilizing computer simulation techniques to optimize device performance. Before joining Texas Instruments, he was a Member of the Technical Staff at UNISYS. where he investigated the physics of transport in thin evaporated films. His post doctoral work in nuclear magnetic resonance was done at Bell Telephone Labs, in Murray Hill, NJ.

**Derek F. Bowers** (A'86–SM'90) was born in Maesteg, Wales, in December 1954. He graduated from the University of Sheffield in 1976 with a B.Sc. in physics and mathematics.

Following a brief employment with the University Space Physics Group, he joined Triad Computing Systems (London) where he worked on robotics and parts inspection systems. In 1978, he joined Bourns (UK) as an Applications Engineer for Precision Monolithics products, and in 1980, transferred to PMI (Santa Clara) as a Senior Design Engineer. Since then, he has held various positions within the company (including Staff Vice President, Design) and following the acquisition of PMI by Analog Devices in 1990 was elected to the position of ADI Fellow. He has some 70 designs in volume production including op-amps, instrumentation amplifiers, audio products, and data conversion circuits. He has authored some 40 technical articles and holds 23 patents related to his design activities.

Mr. Bowers is a member of the Audio Engineering Society.

Mark Dunn received the B.S. degree in electrical engineering from Georgia Tech in 1984 and the M.S. degree in electrical engineering from the University of California at Davis in 1992.

In 1984, he joined the Network Measurement Division (NMD) of Hewlett Packard in Santa Rosa, CA, where he worked on synthesized sources and network analyzers. In 1991, he moved to the CAE group within NMD (later to become HP EEsof) where he has been working on nonlinear device modeling. This work has included efforts in the areas of measurement system design, measurement techniques, extraction algorithms and methodologies, and model generation software. He is currently working on extraction techniques for both the MEXTRAM and VBIC95 bipolar models as well as pulse measurement system design and thermal modeling.

Mark Foisy (S'80-M'89), photograph and biography not available at time of publication,

Ian Getreu (S'65-M'66-SM'75), photograph and biography not available at the time of publication.

Marc McSwain was born on April 9, 1965, in Bryan, TX. He received the B.S.E.E. degree from Texas A&M University, College Station, TX, in 1985, and the M.S.E.E. degree from Louisiana State University, Baton Rouge, LA, in 1988, and the Engineer degree in electrical engineering from the University of Southern California, Los Angeles, CA, in 1992. He is currently pursuing the MBA degree at Santa Clara University, Santa Clara, CA.

In 1990, he joined EEsof, Inc. (now the HP-EEsof Division of the Hewlett-Packard Company), Westlake Village, CA, where he was engaged in microwave device measurement, nonlinear bipolar transistor model creation, parameter extraction methodology development, and nonlinear device model library construction. He joined the semiconductor device modeling group a Meta-Software, Inc., Campbell, CA, in 1994, and is presently a Staff Software Engineer engaged in the research and development of simulation-efficient self-heating compact device models.

Shahriar Moinian (M'88) received the B.S., M.S., and Ph.D. degrees in electrical engineering from University of Southern California, Los Angeles, in 1982, 1983, and 1987, respectively.

From 1987 to 1988, he was with Science Applications International Corporation working on advanced bipolar transistor modeling and processing. In 1988, he joined AT&T Bell Laboratories (now Lucent Technologies Bell Laboratories), Reading, PA, where he is presently a Distinguished Member of Technical Staff. His current interests include modeling, CAD, and circuit and device simulations for silicon bipolar and BiCMOS technologies.

James Parker was born in Welwyn, Saskatchewan, Canada. He received the B.A.Sc. in electronic information systems engineering at the University of Regina, Canada in 1987, and the Master's and Ph.D. degrees in electrical engineering from the University of Waterloo, Canada, in 1990 and 1994, respectively.

He is presently a Senior Process Engineer with the Analog Process Technology Group (APTD) of National Semiconductor in Santa Clara, CA, where he is responsible for improved compact model formulations for bipolar and power MOSFET's and for TCAD support of new process development. Before joining National, he was a Member of Technical Staff at Texas Instruments, Semiconductor Process and Design Center in Dallas, TX, from 1989 to 1990 and again in 1992. He was involved in work on advanced bipolar device modeling for circuit simulation. He has also previously held positions with and consulted for several U.S. and Canadian semiconductor firms, including Northern Telecom, Digital Equipment of Canada, and the National Research Council of Canada.

**David J. Roulston** (M'62–SM'72) was born in England in November 1936. He received the B.Sc. degree from Queen's University, Belfast, N. Ireland, in 1957, and the Ph.D. degree from Imperial College, University of London, in 1962. He was awarded the D.Sc. degree from the University of London in 1994 for his research on the physics of semiconductor devices.

From 1957 to 1958, he was a Scientific Officer at H.M. Underwater Detection Establishment, Portland, Dorset, England. From 1962 to 1967, he was a Research Engineer with CSF, Puteaux, France, working on microwave semiconductor circuits. In 1967, he became an Associate Professor with the Department of Electrical Engineering, University of Waterloo, ON, Canada, and since 1971, he has been a Professor with the same department. He has also held consulting positions with R&D laboratories in Canada, France, Japan, U.K., U.S., and with the UN Industrial Development Organization in India. His research interests are in modeling physical processes in semiconductor devices: specifically bipolar transistors (including microwave, high voltage, and VLSI structures), microwave diodes, photodiodes, MESFET's, and in studying discrete and integrated circuits with a view to the optimization of device performance for a particular circuit function. This work involves both experimental and computer techniques. He is responsible for development of the BIPOLE fast computer program for analysis of bipolar devices, used by semiconductor companies throughout the world. He has published more than 100 technical papers in the above fields and has had six patents awarded in the areas of microwave and optical detector circuits and bipolar devices. He has presented invited seminars or conference papers in 12 countries. He is co-editor of the IEEE Press book Polysilicon Emitter Bipolar Transistors and author of the McGraw-Hill graduate text Bipolar Semiconductor Devices. He is a member of the VBIC95 SPICE committee.

Dr. Roulston is a Fellow of the Institution of Electrical Engineers (England). He was Associate Editor for Bipolar Devices of the IEEE TRANSACTIONS ON ELECTRON DEVICES for two years and is currently on the Honorary Editorial Advisory Board of Solid-State Electronics. For the academic year 1988–1989 he was elected a Visiting Fellow at Wolfson College, Oxford, and has since then made several visits including a 1993/1994 sabbatical leave.

Michael Schröter (M'93) received the Dipl.-Ing. and Dr.-Ing. degrees in electrical engineering and the "venia legendi" in semiconductor devices in 1982, 1988, and 1994, respectively, from the Ruhr-University Bochum, Germany.

From 1983 to 1993, he was with the Semiconductor Devices and Integrated Circuits Group at Ruhr-University Bochum. His main research activities there comprised compact modeling for high-speed bipolar transistors including parameter extraction, development of a mixed-mode three-dimensional

device/circuit simulator, and a CAD tool for circuit design and optimization. The work was financially supported mainly by the German Research Society (DFG) and by Telefunken microelectronic (TEMIC), Heilbronn, Germany. From 1993 to 1996, he was with Northern Telecom (Nortel), Ottawa, Canada, first as Senior Member of Scientific Staff, and later as Team Leader and Advisor. At Nortel he was responsible for bipolar transistor modeling, simulation, and parameter determination. He was also involved in the development of a high-speed bipolar technology and in circuit optimization. Also, in 1994 he was appointed as an Adjunct Research Professor at Carleton University, Ottawa, where he gave a graduate course on bipolar transistor modeling. In 1996 he joined Rockwell Semiconductor Systems, Newport Beach, CA, as a Group Leader responsible for modeling of high-speed semiconductor devices.

Dr. Schroter presently serves on the technical program committee of the BCTM. In 1989, he received the "Eickhoff-Award" for his dissertation.

Paul van Wijnen, photograph and biography not available at the time of publication.

**Lawrence F. Wagner** (M'82) received the B.S. degree in physics from the Massachusetts Institute of Technology, Cambridge, MA, in 1960, the M.S. and Ph.D. degrees from Stanford University, Stanford, CA, in 1969 and 1981, respectively.

From 1961 to 1968, he worked for the U.S. Army Electronics Command in Fort Monmouth, NJ. He also held a post-doctoral position at the University of Hawaii. He is currently a Senior Engineer at the IBM Microelectronics Division, Hopewell Junction, NY, where he has specialized in the modeling and optimization of semiconductor devices since 1981.

Dr. Wagner is a member of the American Physical Society and Sigma Xi.